# Neural Network Architectures for Integrated Circuits

by

## KHYATI NAGRANI 202111031

A Thesis Submitted in Partial Fulfilment of the Requirements for the Degree of

MASTER OF TECHNOLOGY in INFORMATION AND COMMUNICATION TECHNOLOGY to

DHIRUBHAI AMBANI INSTITUTE OF INFORMATION AND COMMUNICATION TECHNOLOGY

July, 2023

#### Declaration

#### Declaration

#### I hereby declare that

- i) the thesis comprises of my original work towards the degree of Master of Technology in Information and Communication Technology at Dhirubhai Ambani Institute of Information and Communication Technology and has not been submitted elsewhere for a degree,

- ii) due acknowledgment has been made in the text to all the reference material used.

KHYATI NAGRANI

#### Certificate

This is to certify that the thesis work entitled "Neural Network Architectures for Integrated Circuits" has been carried out by KHYATI RAJESH NAGRANI for the degree of Master of Technology in Information and Communication Technology at *Dhirubhai Ambani Institute of Information and Communication Technology* under my supervision.

Tapas Kr. Maili

PROF. TAPAS KUMAR MAITI Thesis Supervisor

## Acknowledgments

I would like to express my sincere gratitude and appreciation to the following individuals who have played a crucial role in the completion of my work:

First and foremost, I would like to extend my heartfelt thanks to Prof. Tapas Kumar Maiti, my thesis supervisor. His unwavering support, guidance, and expertise have been instrumental in shaping this research. His insightful feedback and constructive criticism have helped me navigate through various challenges, enabling me to reach new heights in my academic journey. I would also like to extend my deepest appreciation to Prof. Ayan Palchaudhuri, currently faculty of IIT-Bhubaneswar, for his valuable inputs and insightful discussions throughout this research endeavor. His vast knowledge and expertise in the field have been truly inspiring, pushing me to explore new avenues and think critically.

I would also like to extend my thanks to my dear friends and PhD scholar, Gulafsha Bhatti. Their friendship, and intellectual discussions have been a source of inspiration and motivation for me.

I am deeply grateful to my parents, Saroj Nagrani and Rajesh Nagrani for their unwavering love, encouragement, and constant belief in my abilities. Their endless support, understanding, and sacrifices have been the foundation of my success, and I am forever indebted to you for the opportunities you have provided me. Furthermore, I would like to express my gratitude to my brother, Hriday Nagrani. His encouragement, motivation, and belief in me have been invaluable throughout this journey.

Lastly, I would like to acknowledge the support and encouragement I received from all my friends and well-wishers who have cheered me on during this academic pursuit. Their friendship, understanding, and motivation have made this journey all the more fulfilling.

To all those mentioned above, as well as to anyone else who has contributed to my work in any way, I offer my heartfelt appreciation. Their guidance, support, and belief in me have been the driving force behind the successful completion of my thesis, and I am truly grateful for their presence in my life.

## Contents

| Al | Abstract v |         |                                                           |     |

|----|------------|---------|-----------------------------------------------------------|-----|

| Li | st of ]    | Princip | al Symbols and Acronyms                                   | v   |

| Li | st of '    | Tables  |                                                           | vi  |

| Li | st of I    | Figures | 3                                                         | vii |

| 1  | Intr       | oductio | on                                                        | 1   |

|    | 1.1        | Neur    | on and Neural Network                                     | 3   |

|    | 1.2        | Artifi  | icial Neuron and Artificial Neural Network                | 4   |

|    | 1.3        | Appli   | cations of Artificial Neural Network                      | 6   |

|    | 1.4        | Chip    | Design for NNs                                            | 6   |

|    | 1.5        | NNs a   | as Co-Processor                                           | 7   |

|    | 1.6        | Aims    | and Objectives                                            | 8   |

| 2  | Rev        | iew of  | Neural Network Architectures                              | 10  |

|    | 2.1        | Revie   | w of Adder Design                                         | 10  |

|    |            | 2.1.1   | Comparison of Adders on Basis of Area, Power, and Delay . | 10  |

|    | 2.2        | Revie   | w of Multiplier Design                                    | 12  |

|    |            | 2.2.1   | Comparative Analysis of Several Multipliers               | 12  |

|    | 2.3        | Revie   | w of Activation Function Design                           | 15  |

|    |            | 2.3.1   | Activation Functions for Neural Networks                  | 15  |

|    |            | 2.3.2   | ReLU, Linear Saturated, and Other Activation Functions:   |     |

|    |            |         | Comparisons                                               | 16  |

|    |            | 2.3.3   | Conclusion for Activation function design                 | 17  |

|    |            | 2.3.4   | Comparison of ReLU and Sigmoid                            | 18  |

|    | 2.4        | Revie   | w of Neural Networks Design                               | 20  |

|    |            | 2.4.1   | Artificial Neural Networks                                | 20  |

|    |            | 2.4.2   | Energy-Efficient VLSI Architectures                       | 21  |

|    |            | 2.4.3   | Memory Organization Techniques                            | 21  |

|    |        | 2.4.4   | Algorithmic Innovations                | 21 |

|----|--------|---------|----------------------------------------|----|

|    |        | 2.4.5   | Impact on Real-World Applications      | 22 |

|    |        | 2.4.6   | Conclusions for Neural Network Design  | 22 |

| 3  | Imp    | lemen   | tation of Neural Network Architectures | 23 |

|    | 3.1    | Imple   | mentation of Adder                     | 23 |

|    | 3.2    | Imple   | mentation of Multiplier                | 24 |

|    | 3.3    | Imple   | mentation of SISO NN Architecture      | 26 |

|    | 3.4    | Imple   | mentation of MISO NN Architecture      | 27 |

|    | 3.5    | Imple   | mentation of MIMO NN Architecture      | 29 |

| 4  | Neu    | ıral Ne | tworks Layout                          | 31 |

|    | 4.1    | Desig   | n Flow                                 | 31 |

|    | 4.2    | Desig   | n Tools                                | 32 |

|    | 4.3    | Detail  | s of Tools Used                        | 33 |

|    | 4.4    | Open    | LANE                                   | 42 |

|    |        | 4.4.1   | OpenLANE Configuration Variables       | 43 |

|    |        | 4.4.2   | Required Configuration Variables       | 43 |

|    |        | 4.4.3   | Optional Configuration Variables       | 43 |

|    |        | 4.4.4   | Details of Configuration Variables     | 44 |

|    | 4.5    | Tape-   | Out Details                            | 45 |

|    | 4.6    | Tape-   | Out                                    | 46 |

|    | 4.7    | Comp    | parison with Published Work            | 50 |

| 5  | Con    | clusio  | ı                                      | 51 |

| Re | eferei | nces    |                                        | 53 |

## Abstract

This thesis presents the architecture design and implementation of neural networks (NNs) for integrated circuit design. The architecture consists of adders, multipliers, and rectified linear unit (ReLU) blocks. Three architectures, namely, Single-In Single-Out (SISO), Multiple-In Single-Out (MISO), and Multiple-In Multiple-Out (MIMO) are developed. In neural networks, weight values are necessary and they are supplied from a memory source. The weight values were prepared by training the NNs model on software. Finally, the SISO, MISO, and MIMO neural-networks were taped out. These architectures can be used for intelligent co-processor development.

## **List of Tables**

| 2.1 | Performance analysis of various Adders[17] | 12 |

|-----|--------------------------------------------|----|

| 4.1 | Optional configuration variables           | 44 |

| 4.2 | Tape-Out details                           | 45 |

| 4.3 | Comparison with exisiting works            | 50 |

# List of Figures

| 1.1 | A biological neuron [7].                                                | 3  |

|-----|-------------------------------------------------------------------------|----|

| 1.2 | A biological neural network (NN) [8]                                    | 4  |

| 1.3 | Architecture of three-layer ANN                                         | 5  |

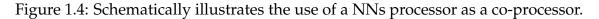

| 1.4 | Schematically illustrates the use of a NNs processor as a co-processor. |    |

|     |                                                                         | 7  |

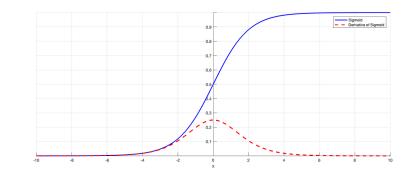

| 2.1 | Depicts Sigmoid function and it's derivative [29].                      | 19 |

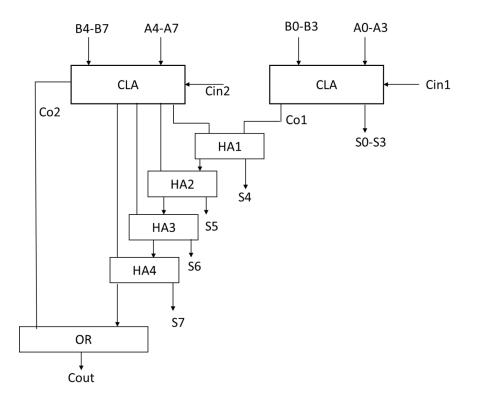

| 3.1 | Depicted the architecture of a carry increment adder (CIA)              | 24 |

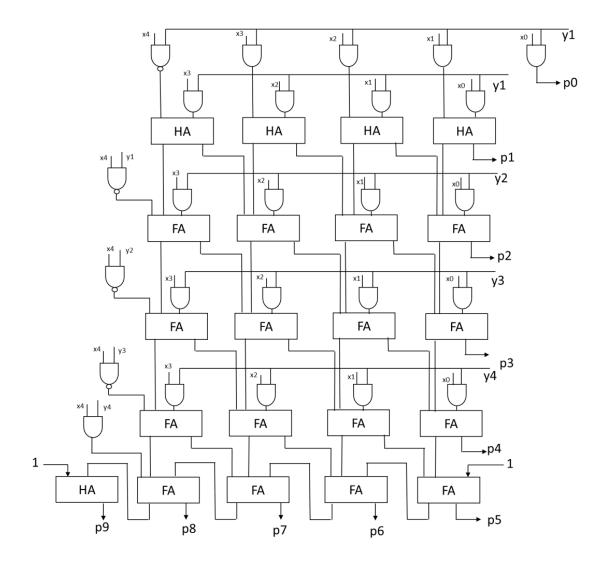

| 3.2 | Architecture of Multiplier                                              | 25 |

| 3.3 | SISO architecture.                                                      | 26 |

| 3.4 | Depicted the simulated waveform obtained using SISO architec-           |    |

|     | ture                                                                    | 27 |

| 3.5 | Architecture of MISO.                                                   | 28 |

| 3.6 | Simulated waveform obtained using MISO architecture                     | 28 |

| 3.7 | Depicted the developed MIMO Architecture.                               | 29 |

| 3.8 | Simulated responses of MIMO architecture.                               | 30 |

| 4.1 | Tools used for implementation.                                          | 33 |

| 4.2 | Workflow of yosys.                                                      | 35 |

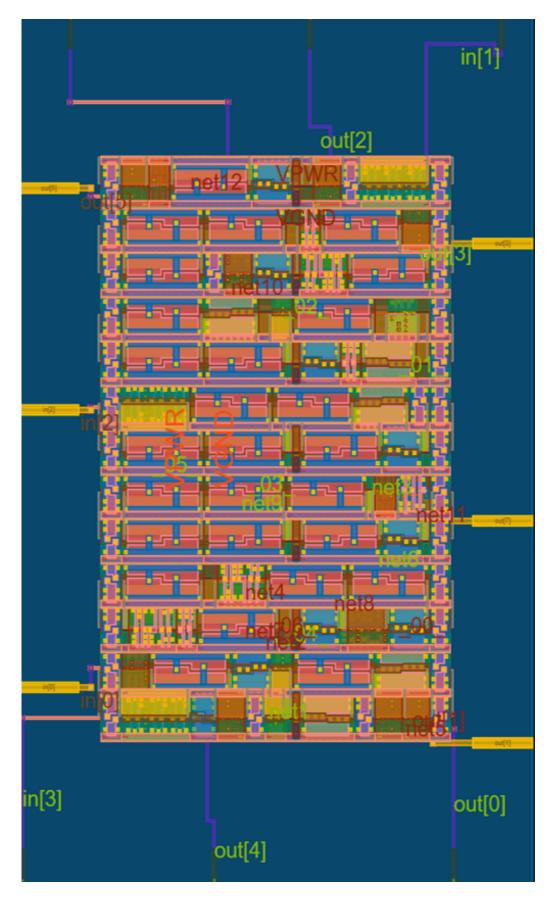

| 4.3 | Tape-out of SISO.                                                       | 47 |

| 4.4 | Tape-out of MISO.                                                       | 48 |

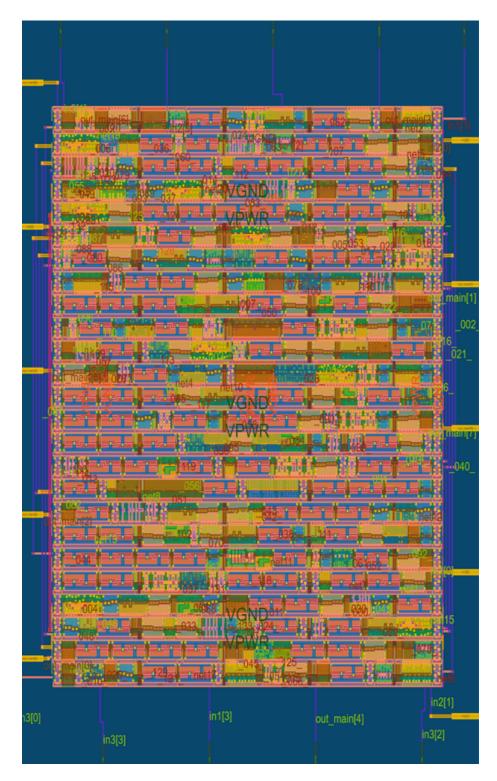

| 4.5 | Tape-out of MIMO.                                                       | 49 |

## CHAPTER 1 Introduction

Neural networks (NNs) were implemented using both the software and hardware [1], [2]. However, the hardware level implementation of neural network (NN) improves the speed, efficiency, real-time processing, power efficiency, and scalability in comparison to the software level implementation. The improvement details are discussed below:

Speed and Efficiency: In comparison to software solutions, NN hardware achieved considerable speed and efficiency benefits [1], [2], [3]. To speed up neural network computations, specialised hardware can be proposed, such as application-specific integrated circuits (ASICs) [3]. Faster inference and training times are achieved by using specialised hardware like field-programmable gate arrays (FPGAs), graphics processing unit (GPU) that take advantage of parallelism and optimise the execution of matrix operations. It may also result in less power usage, increasing its energy efficiency.

Real-time processing: Low-latency (Latency refers to the delay or the time it takes for a system to respond to a given input or stimulus. It is the time interval between initiating an action or request and receiving the corresponding response or output) processing is necessary for several applications, including real-time decision-making systems, robots, and autonomous vehicles. NN hardware solutions offer the speed and responsiveness required to satisfy real-time needs [4]. The system may analyse data and produce predictions in real-time without depending on the constraints of software-based systems by outsourcing the computing effort to specialised hardware.

Power Efficiency: Neural network calculations are computationally demanding, especially for complicated or large-scale problems. General-purpose processors (CPUs) or graphics processing units (GPUs) are frequently used in softwarebased systems, which may require more power to run the calculations [5]. In contrast, neural network operations may be extensively optimised for hardware implementations, which reduces power use. Hardware neural network implementations are ideally suited for use in embedded systems and edge computing settings (Proximity-based data processing, decentralizing from remote clouds.), according to research [6]. In these cases, neural networks are used on hardware with constrained storage and processing power. By implementing neural networks on specialized hardware, the primary processor offloads computational burdens, creating a separation of tasks and freeing up resources for other functions [6].

Scalability: Neural network hardware implementations can be designed to effectively scale with the increasing demands of neural network processing [2]. Implementation of NN hardware can be improved and optimized to handle larger models and datasets as the requirements for neural network computations grow. Scalability can be provided via hardware designs like systolic arrays or specialised deep learning accelerators and support for parallel processing, enabling faster training and inference on increasingly complex neural networks. Scalability, in the context of neural network hardware designs, refers to their ability to effectively handle larger and more intricate models and datasets as the demand for neural network processing grows. It encompasses the capacity to manage increased computational loads and accommodate expanding requirements.

One hardware design that supports scalability is the systolic array, commonly utilized for accelerating matrix operations in neural networks. A systolic array comprises a synchronized array of processing elements interconnected in a regular pattern, enabling efficient flow of data through the array. Notably, systolic arrays excel in parallel processing, making them well-suited for performing matrix multiplications, convolutions, and other vital operations in neural networks.

Systolic arrays offer scalability through the parallel execution of operations across multiple processing elements. As neural networks become larger and more complex, systolic arrays can be scaled up by expanding the array's dimensions or increasing the number of processing elements. This allows for distributed computation and optimal resource utilization, enabling faster training and inference on larger neural networks.

## 1.1 Neuron and Neural Network

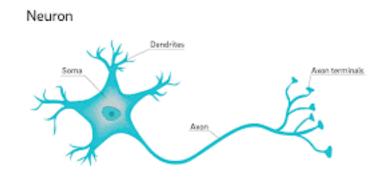

The fundamental units of an animal's nervous system, including the human nervous system, are called biological neurons. Their job is to process and send information via electrical and chemical signals. They are specialised cells which consist of a cell body, dendrites, and an axon make up each neuron. While the axon sends electrical signals from the cell body to other neurons or muscles, the dendrites receive alerts from other neurons or sensory receptors. Figure 1.1 shows diagram of biological neuron [7]. A neuron produces an electrical impulse known as an action potential when it receives a signal from another neuron or a sensory receptor. The neurotransmitters, molecules that send signals to subsequent neurons in a chain are released due to the action potential moving down the axon. Movement, sensation, perception, learning, and memory are just a few of the numerous brain activities that depend on neurotransmitter-mediated communication between neurons. Neuronal communication dysfunction has been linked to a variety of neurological and psychiatric disorders, such as Alzheimer's disease, Parkinson's disease, and depression.

Figure 1.1: A biological neuron [7].

A biological neural network is called the intricate web of neurons and synapses that makes up the nervous system of living things. Specialised cells called neurons are in charge of sending electrical and chemical signals throughout the body to convey information. The processing and integration of sensory data, the creation of motor orders, and the coordination of body activities are all made possible by the complex networks of neurons that make up the brain. Neuroplasticity is the ability of these networks to adapt and change throughout time in response to experiences and stimuli.

Figure 1.2: A biological neural network (NN) [8].

The neural network's ability to function depends heavily on the synapses or connections between neurons. The strength and effectiveness of these connections, which allow for the passage of information between neurons, can be altered by various variables, including experience and learning [9]. Figure 1.2 shows picture of a biological neural network. [8] The biological neural network, which underlies the operation of the nervous system as well as the behaviour and cognition of living animals is an immensely intricate and dynamic system.

## **1.2** Artificial Neuron and Artificial Neural Network

The basic components of an artificial neuron includes the following:

- An activation function is defined as an eqation that calculates the value of output of the neuron on the basis of the weighted inputs.

- Inputs are numerical values that reflect the data to be processed.

- Weights are numerical values that indicate the strength of the link between the inputs and the neuron.

The appropriate weights are multiplied with the inputs, and the resulting values are summed. The total is then passed through the activation function, which generates the output of the neuron. This output can either be used as the final output of the neural network or shared with other neurons for communication purposes [10]. The activation function has various forms, such as step, sigmoid, ReLU (Rectified Linear Unit), and others. The choice of activation function can significantly affect the performance and behavior of the neural network.

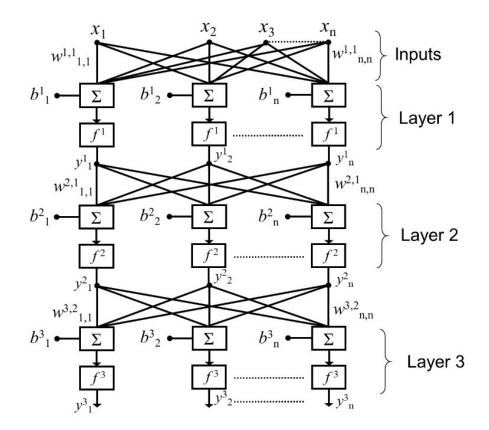

Artificial neural networks are created by joining artificial neurons together. These networks can then be trained using a variety of algorithms to identify patterns in the input data and generate predictions based on those patterns [11]. A machine learning technique called an artificial neural network (ANN) is modelled on the basis of the biological neural networks that make up the human brain [12]. A large number of neurons, arranged in layers, make up an ANN. Each neuron takes in one or multiple input signals, computes, and then sends its output to other neuron in the layer below as mentioned in Figure 1.3.

Figure 1.3: Architecture of three-layer ANN.

An ANN typically has three layered structure of neurons which are an input layer, a few to many hidden layers, and lastly the output layer [13]. Raw data is delivered to the input layer, which is processed by the hidden layers. The output layer creates the network's ultimate output, which may be a classification, a prediction, or another type of judgement.

The signal strength of the interconnection between two neurons in an ANN defines how much influence one neuron has on the other since the relations between the neurons in an ANN are often weighted [14]. The backpropagation technique uses weights that are modified during training to reduce the discrepancy between the NN's output and the expected output. Predictive analytics, natural language processing, image and audio recognition, and other fields all make use of ANNs.

## **1.3** Applications of Artificial Neural Network

Neural networks (NN) find applications across diverse fields such as pattern recognition, natural language processing, medical applications, etc., offering various uses as powerful tools. Some notable applications include:

1. Pattern Recognition: NNs excel in recognizing patterns in voice, images, and other media. They are extensively employed in facial recognition technology, enabling the identification of faces in images or videos.

2. Natural Language Processing (NLP): NNs play a crucial role in NLP applications such as speech recognition, text-to-speech conversion, language translation, and sentiment analysis [15]. They enable the understanding and interpretation of human language.

3. Medical Applications: NNs are utilized in predictive modeling to discover patterns in data and generate predictions based on those patterns. For instance, they can leverage a patient's medical history and symptoms to forecast stock prices or consumer behavior.

Overall, NNs possess versatile applications and serve as valuable tools across various industries. Their ability to learn from data and identify trends makes them highly beneficial in a wide range of domains.

## 1.4 Chip Design for NNs

The process of generating ICs that are optimised for neural network (NNs) processing activities are known as NN chip design. By carrying out numerous computations in parallel, these chips are made to speed up the analysis of neural network algorithms.

The development of NNs chips is a complex process that involves both hardware and software elements. The physical layout of the chip involves placing transistors, logic gates, and memory cells. On the other hand, developing the algorithms used to program the device falls under the responsibility of the software components.

Field-programmable gate arrays (FPGAs), which enable testing and architecture modifications before manufacturing, are frequently used to design NN chips. Once the chip's design is finalized, it undergoes a manufacturing process known as photolithography, which involves etching the chip's intricate pattern onto a silicon wafer.

Due to the growing need for quicker and more effective neural network pro-

cessing, the design of NN chips is a crucial field of research. These chips have uses in many different industries, including driverless vehicles, natural language processing, and picture and audio recognition.

## 1.5 NNs as Co-Processor

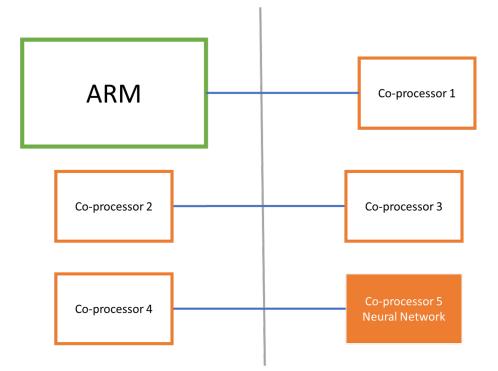

In some applications, NNs can be a co-processor (see Figure 1.4) to offload computation from the primary processor. This is especially helpful in applications where a real-time reaction is essential or where the central processor's processing capability is constrained.

Applications for processing images and videos are one instance of using NNs as a coprocessor. To increase the speed of the processing of this data, NNs can be trained to recognise patterns in photos and videos. This can help picture recognition, and other computer vision tasks run more quickly and accurately. Applications for natural language processing (NLP) are yet another illustration. The processing of vast amounts of text data, such as language translation, sentiment analysis, and text classification, can be sped up using NNs. This can aid in enhancing the efficiency of NLP tasks by increasing their speed and accuracy.

In conclusion, by offloading work off the primary processor, the use of NNs as coprocessors can aid in enhancing the performance of some applications. This

can be especially helpful in applications that demand a quick reaction or a lot of processing power.

## **1.6** Aims and Objectives

In recent years, the field of artificial intelligence has witnessed remarkable advancements, particularly in the realm of NNs [16]. Neural networks, with their ability to learn and adapt, have revolutionized numerous domains, from computer vision to natural language processing [3]. However, their potential is often limited by the constraints of traditional processing architectures. By harnessing the power of neural networks as co-processors, we can unlock unprecedented opportunities for accelerated computations, enhanced pattern recognition, and optimized system design.

The integration of neural networks as co-processors in computing systems presents a paradigm shift in leveraging AI capabilities. By investigating the specific benefits, we aim to provide a comprehensive understanding of why neural networks as co-processors are essential for accelerating computations and advancing system design.

Enhanced Computational Performance: The incorporation of neural networks as co-processors enables the offloading of computationally intensive tasks from the primary processor, thereby reducing the overall processing time. Neural networks excel at parallel processing, allowing for the efficient execution of complex algorithms, such as image recognition, speech synthesis, and natural language understanding. By distributing computational workloads across multiple processors, system performance is significantly enhanced, leading to faster results and improved user experience.

Accelerated Pattern Recognition: Neural networks possess an innate ability to recognize complex patterns and extract meaningful information from large datasets. By leveraging neural networks as co-processors, we can leverage their parallel processing capabilities to expedite pattern recognition tasks. Whether it is identifying objects in images, analyzing financial data, or detecting anomalies in sensor readings, neural networks can perform these tasks with remarkable speed and accuracy. The integration of neural networks as co-processors offers unparalleled potential for real-time decision-making in applications that require rapid and precise pattern recognition.

Optimal System Design: Designing hardware architectures solely based on traditional processing units can be suboptimal for AI-centric applications. Neural networks have unique architectural requirements and specialized instructions that are distinct from conventional processors. By incorporating neural networks as co-processors, we can design specialized hardware that is tailored to the specific needs of neural network computations. This leads to improved energy efficiency, reduced memory bandwidth requirements, and better utilization of computational resources. Moreover, the flexibility provided by co-processors allows for seamless integration of evolving neural network models, ensuring compatibility with future advancements in AI technology.

In summary, the integration of neural networks as co-processors brings forth a host of advantages that revolutionize computational performance and system design. From enhanced computational speed to accelerated pattern recognition and optimized system architectures, neural networks empower us to overcome the limitations of traditional processing units. By embracing neural networks as co-processors, we unlock a new era of AI-driven applications with improved efficiency, accuracy, and the potential for groundbreaking innovations. Chapter 2 presents a literature survey on ML architecture, examining the various modules employed within these architectures. Chapter 3 focuses on the implementation of the surveyed ML architecture. We describe the ASIC design flow in Chapter 4. Thesis work is summarized in Chapter 5.

## CHAPTER 2 Review of Neural Network Architectures

Over the past few years, the field of VLSI architecture for neural networks has witnessed significant advancements, fueled by the increasing demand for efficient and powerful hardware implementations of artificial intelligence algorithms. As neural networks become a cornerstone of numerous applications, ranging from image recognition to natural language processing, researchers have focused their efforts on developing novel architectures to address the challenges of processing large-scale neural networks with high computational demands.

This chapter presents a comprehensive literature review that explores various aspects of VLSI architecture for neural networks, including activation functions and modules related to microarchitecture. Through an extensive survey of research papers, we delve into the state-of-the-art techniques and methodologies employed by researchers to enhance the efficiency and performance of neural network hardware.

## 2.1 Review of Adder Design

Numerous VLSI architectures have been proposed over the years to improve the area efficiency of adders, considering their essential role in modern digital systems. This section aims to explore and compare the area characteristics of various adder architectures, shedding light on their strengths and limitations. Following table shows that CIA is better choice the others

#### 2.1.1 Comparison of Adders on Basis of Area, Power, and Delay

Standard cells and FPGAs (Field Programmable Gate Arrays) are examples of cell-based design methodologies. These techniques, simultaneously with flexible hardware synthesis, are vital for high productivity in ASIC (Application Specific Integrated Circuit) design. With O(n) area and O(n) latency, the RCA (Ripple

Carry Adder) is the simplest but slowest adder, where n is the operand size in bits.

CSA (Carry Select Adder) has an O(log n) latency and an O(n) area. In an n-bit adder, n/2 multiplexers are chosen using a carry signal.

The document (particularly for this subsection) studied outlines the adder topology design. The following adder structures are employed in that work: CIA (Carry Increment Adder), CSkA (Carry Skip Adder), CBA (Carry Bypass Adder), and CSA are all examples of ripple adders [17]. One drawback of RCA adder is that its latency increases proportionally with the length of the numbers being added, which limits its efficiency when handling large bit numbers [18].

The performance of the RCA is constrained as the number of bits, increases since the ripple carry adder's latency, is directly proportional to number of bits. In order to establish an impartial testing environment, the simulations have been conducted using a comprehensive input signal pattern that covers every probable transition for all the adders. Its frequencies span from 10 to 500MHz, and its input and output capacitance are each set to 10pf. Adder topologies are assessed based on their ability to withstand challenges related to area, latency, and power consumption. According to the power distribution graph, the carry save adder experience the most power dissipation. CIA and RCA have the lowest power dissipation. CIA, and CSA both have the same minimum latency [19]. In this work, thorough investigations of adder topologies with 120 nm CMOS technology have been done. Area, latency, and power dissipation were used for the comparison. The transistor-level design has taken parasitic layout effects into account. The investigations include performance analysis, simulation results, and comparisons. CLA and CIA, which are apt for high-performance circuits, provide the optimum balance between area, delay, and power dissipation, according to the findings of the analysis.

#### Conclusion for adder design

The RCA, CSkA, and CBA with the fewest gates, and the greatest delay are the most basic adder topologies appropriate for low-power applications [20]. From the table given below it can concluded that, Carry Increment Adder achieves better performance in terms of area and delay compared to that of other adder topologies [17].

After a thorough research, it has been determined that the CIA demonstrates excellent performance in terms of area efficiency. Consequently, the CIA has been selected as the preferred choice for this particular work.

|   | Design                 | Area(LUTs) | Area(Slices) | Delay(ns) |

|---|------------------------|------------|--------------|-----------|

| 1 | Ripple Carry Adder     | 8          | 5            | 2.191     |

| 2 | Carry Skip Adder       | 8          | 6            | 2.267     |

| 3 | Carry Increment Adder  | 8          | 5            | 1.907     |

| 4 | Carry Look Ahead Adder | 10         | 5            | 2.266     |

| 5 | Carry Save Adder       | 13         | 9            | 1.433     |

| 6 | Carry Select Adder     | 8          | 5            | 2.588     |

| 7 | Carry Bypass Adder     | 12         | 6            | 3.160     |

Table 2.1: Performance analysis of various Adders[17].

## 2.2 Review of Multiplier Design

Subsequent subsection describes the extensive research conducted on multiplier architecture. These findings are summarized and analyzed in section below.

#### 2.2.1 Comparative Analysis of Several Multipliers

First document discusses the development of a generic HDL code for a fast Baugh Wooley multiplier. The conventional Baugh Wooley multiplier architecture is modified by replacing the ripple carry adder in the final stage with a Linear Carry Select Adder. The post-synthesis results of the modified architecture are compared with the conventional Baugh Wooley architecture and the default multiplier architecture generated by a synthesis tool. The comparison is based on various characteristic parameters such as propagation delay, area, and power consumption. The results demonstrate that the modified Baugh Wooley architecture is faster than both the conventional architecture and the default synthesis-generated architecture, particularly for larger operand sizes. This improvement in speed is significant [21]. The paper provides a detailed explanation of the Baugh Wooley multiplication algorithm and outlines the steps to create a generic HDL code for a fast NxN Baugh Wooley multiplier. This approach allows designers to easily generate Baugh Wooley multipliers of any operand size by simply modifying the operand size parameter, thereby reducing design efforts. In conclusion, the modified Baugh Wooley architecture offers superior performance in terms of both delay and power-delay product compared to the conventional architecture and the default synthesis-generated architecture. It presents a valuable solution for digital ASTC designers seeking efficient and fast Baugh Wooley multipliers of different sizes [21].

The Modified Baugh-Wooley (MBW) multiplier approach is widely employed in digital signal processing and hardware design to achieve high-speed multiplication tasks. It offers several advantages over conventional multiplication methods such as the array multiplier. Research in this field has identified multiple benefits associated with the MBW.

The MBW multiplier approach exhibits lower complexity in implementation compared to alternative methods. It achieves this by reducing the number of partial product terms and overall complexity in the multiplication process. This is accomplished by breaking down incomplete products into smaller sections and employing advanced algorithms to generate the final result. The reduction in complexity has several implications, including decreased hardware requirements and reduced power consumption [42].

To elaborate on the previous statement, the reduction in complexity in the MBW multiplier leads to a decrease in hardware requirements. In traditional multiplication methods like the array multiplier, the number of partial products grows exponentially with the bit size of the operands, resulting in a larger hardware footprint. However, the MBW multiplier breaks down these partial products into smaller chunks, reducing the number of required components. This not only saves physical space but also leads to a more efficient utilization of hardware resources. Furthermore, the decreased complexity in the MBW multiplier results in reduced power consumption. The simplified circuitry and reduced number of partial products contribute to lower power requirements during the multiplication process. This is particularly beneficial in power-constrained applications, such as mobile devices or embedded systems, where minimizing power consumption is crucial to enhance battery life and overall energy efficiency.

The MBW multiplier is built to perform multiplication operations at fast speeds. It takes advantage of effective parallel processing strategies, including carry-lookahead and carry-save adders, to speed up the calculation of the result. The MBW multiplier may lower the multiplication delay and enhance system performance as a whole. Effective use of hardware resources: By lowering the required number of logic gates for the multiplication operation, the MBW multiplier effectively uses hardware resources. In order to optimise the design, symmetry and symmetrybreaking techniques are used. The MBW multiplier provides improved resource allocation and may be more cost-effective in chip space and power consumption by effectively using hardware.

Due to the MBW multiplier's great scalability, expanding it to support multipliers with parallel processing or larger word sizes is simple. It is apt for a wide range of applications, including image processing, digital signal processing, and communication systems, due to its scalability.

The Baugh-Wooley multiplier, Modified Baugh-Wooley (MBW) multiplier, and Wallace multiplier are compared in terms of area, depending on the implementation details and the technology used. Because the MBW multiplier is an advance over the Baugh-Wooley method but does not significantly increase hardware complexity, the Baugh-Wooley multiplier and the MBW multiplier often have similar area requirements [22]. Both algorithms follow a similar methodology and can achieve similar area efficiency. In contrast, the Wallace multiplier often needs more space than the Baugh-Wooley and MBW multipliers. The Wallace multiplier is renowned for its high-speed multiplication, but it does it by employing a tree-like structure with many partial products and complicated hardware. Less complicated hardware: The Baugh Wooley multiplier can be modified to lower the hardware requirements. Lower power consumption may also be achieved through simplified technology and increased effectiveness. This is crucial for battery-operated and mobile devices, where power efficiency is a major issue. The MBW multiplier may be improved such that it is more readily scalable and can multiply values with wider bit widths effectively. Applications that need highprecision computations or work with big data sets might benefit from this flexibility. It is possible to create a modified Baugh Wooley multiplier that works with a variety of number representations, such as signed numbers and floating-point formats. The multiplier may be utilised in a larger variety of applications thanks to its adaptability.

When considering area efficiency as the primary concern in multiplier design, the Modified Baugh Wooley (MBW) multiplier typically outperforms the Wallace multiplier. The area efficiency of a multiplier refers to how effectively it utilizes hardware resources to perform the multiplication operation.

The MBW multiplier is designed based on the concept of Modified Booth Encoding (MBE). It leverages the properties of MBE to reduce the number of partial product terms generated during multiplication. This reduction in partial product terms leads to a decrease in the overall hardware requirements, resulting in improved area efficiency.

In terms of area efficiency, the MBW multiplier offers advantages over the Wallace multiplier due to its ability to reduce the number of partial product terms and minimize the associated hardware requirements. This reduction in hardware translates to a more compact and efficient design. Hence, the MBW multiplier is often more area-efficient when compared to the Wallace multiplier if area efficiency is the primary consideration.

## 2.3 Review of Activation Function Design

Activation functions play a crucial role in shaping the behavior and expressive power of neural networks. In this section, we explore a wide range of papers that investigate different activation functions and their impact on VLSI architectures. From traditional functions such as sigmoid and tanh to more recent advances like rectified linear units (ReLU). We analyze their properties, computational complexity, and suitability for hardware implementations [23].

#### 2.3.1 Activation Functions for Neural Networks

With the emergence of various deep learning (DL) architectures, NNs have proven to be effective in addressing complex real-world challenges across different sectors. Activation functions (AFs) play a crucial role in these NNs architectures, facilitating computations between hidden layers and output layers to achieve stateof-the-art results. This work aims to provide insights into the current usage of activation functions in deep learning applications and highlights recent advancements in this field. The unique contribution of the work lies in its comprehensive compilation of the majority of activation functions utilized in NNs, as well as its analysis of their current utilization trends in real-world deep learning implementations compared to cutting-edge research findings. This compilation aims to facilitate the selection of the most suitable activation function for specific applications that are ready for deployment. It stands out as the first article to compare the practical trends in activation function usage with the findings from existing literature in deep learning research. This topicality is significant considering that most research publications on activation functions primarily focus on similar efforts and outcomes.

This section provides an overview of the activation functions currently employed in deep learning applications and highlights recent trends in their utilization in real-world deep learning deployments, contrasting them with cutting-edge research findings. This study identified several important activation functions used in deep learning applications, including variations of the original ReLU (Rectified Linear Unit). Nwankpa and colleagues also provided a concise overview of deep learning and activation mechanisms [24]. Activation functions play a crucial role in neural networks by computing the weighted sum of inputs and biases to determine if a neuron should fire. The Softmax function is commonly used in multi-class models to provide probabilities for each class, with the highest probability assigned to the target class. To mitigate overfitting in neural networks, the rectified linear unit (ReLU) activation function has been chosen.

The researchers affirm that their findings align with previous research in the field, emphasizing that activation functions regulate neural network outputs and can be linear or non-linear, often referred to as transfer functions. They suggest that future studies should explore these cutting-edge functions on successful architectures using standardized datasets to evaluate potential performance improvements [25]. Non-linear modules in deep learning methods transform initial inputs into more abstract representations, often involving complex learned functions. This study offers a comprehensive overview of activation functions used in deep learning and highlights current trends based on unpublished cutting-edge research findings.

Activation functions have the ability to enhance pattern learning in data, enabling automated feature detection. This justifies their utilization in hidden layers of neural networks and their applicability across different domains. Looking ahead, compounded activation functions hold promise for future research in this area, as activation functions have evolved over time.

## 2.3.2 ReLU, Linear Saturated, and Other Activation Functions: Comparisons

Stursa *et.al.*, compared two types of linear activation functions used in feedforward neural networks for approximating nonlinear systems: symmetric linear saturated function and rectifier linear unit (ReLU) function. The authors aim to evaluate their performance, convergence speed, and computational demands [26]. The experiments are conducted using one hidden layer with varying numbers of neurons, and strict criteria are applied, including the use of the Levenberg-Marquardt algorithm for training and the Nguyen-Widrow algorithm for initialization. Three benchmark nonlinear systems are selected for approximation, and training data is generated by applying a colored input signal, and computing the corresponding output. The comparison is based on the convergence speed for a fixed error function value and the performance over a constant number of epochs. The results show that both the activation functions exhibit similar performance and convergence speed, with only small differences observed. Although the symmetric linear saturated activation function yields a lower median error function value across different numbers of neurons, the ReLU function proves to be capable of effectively modeling nonlinear systems as well. They also discussed the complexity of training neural networks with linear activation functions [26]. It concludes that the ReLU function, due to its comparable performance and potential computational complexity decrease, can be a suitable choice for nonlinear system modeling in process control and automation applications.

Another study compared the effects of different activation functions (AFs) in Artificial Neural Networks (ANNs) on regression and classification tasks using various datasets. A total of 11 AFs, including 10 commonly used in the literature and a newly proposed Square function, were evaluated. Three different ANN architectures were employed for each dataset. The study examined the success rates in test data and the duration of training for each AF [27]. The results showed that the choice of AF significantly impacted the performance of ANNs across different datasets and architectures. ReLU emerged as the most successful AF for general purposes. In image datasets, the Square function performed better than other AFs when combined with ReLU in architectures involving convolutional layers. Furthermore, the study highlighted the importance of batch normalization before applying AFs. By keeping the inputs to AFs within certain bounds, batch normalization eliminated the limitations of both limited and unlimited AFs. It was found that batch normalization positively affected the results, especially for unlimited AFs.

Overall, the findings emphasize the significance of selecting appropriate AFs in ANNs, as they can greatly influence regression and classification performance, particularly in different types of datasets. ReLU is generally recommended as a reliable choice, while the Square function shows promise for image datasets when used alongside ReLU. The use of batch normalization is also beneficial for improving results, particularly with unlimited AFs [27].

#### 2.3.3 Conclusion for Activation function design

ReLU has the ability to create sparse activations, which means it can set certain neuron outputs to zero, making the data representation more effective. ReLU can also experience a condition known as dying ReLU, in which certain neurons remain permanently inactive (outputting zero) due to this issue.

The sigmoid function is denoted by the formula f(x) = 1/(1 + e(-x)), where x represents the function's input. The input is mapped to the range [0, 1] via a smooth, S-shaped curve. In binary classification situations, where the objective is to forecast probabilities between 0 and 1, sigmoid activation is frequently utilised in the output layer. The input is condensed to a narrow range, making it appropriate for modelling probabilities.

However, sigmoid experiences the Vanishing gradient problem, particularly in deep networks, where the gradients can shrink to extremely tiny values and cause

training to converge slowly. When inputs are far from zero, sigmoid activations can also result in the "gradient saturation" issue, which slows learning by bringing gradients near to zero. In binary classification situations, where the objective is to forecast probabilities between 0 and 1, sigmoid activation is frequently utilised in the output layer. It reduces the input's range, which makes it appropriate for modelling probabilities.

#### 2.3.4 Comparison of ReLU and Sigmoid

#### 2.3.4.1 Advantages of ReLU over Sigmoid:

Although Rectified Linear Unit (ReLU) and Sigmoid are both frequently used activation functions in neural networks, they each offer unique qualities and benefits. ReLU has the following benefits over sigmoid:

1. ReLU is a simpler function than the sigmoid function since it just requires a threshold operation and no exponential computations, making it more efficient. ReLU is more efficient to calculate thanks to its simplicity, especially when working with large-scale neural networks [24].

2. For inputs that are noticeably positive or negative, the gradient becomes extremely modest since sigmoid activation saturates at the function's extreme ends. The vanishing gradient problem, which results in sluggish convergence and challenges while training deep neural networks, might be brought on by this saturation. ReLU, on the other hand, is linear for positive inputs and does not experience saturation. The gradient can flow more freely as a result, hastening convergence.

3. The Rectified Linear Unit (ReLU) activation function exhibits sparsity, where it selectively activates a subset of neurons while keeping others dormant. This characteristic enables a more efficient representation of data within a neural network. By reducing unnecessary calculations, sparse activation decreases the overall complexity of the network and helps mitigate overfitting by promoting generalization.

4. Avoiding the exploding gradient problem: Because of the sigmoid function's constrained range, it is possible for gradients to explode during backpropagation, leading to unpredictable results. Since ReLU lacks an upper constraint, gradients can spread more readily without leading to instability.

5. ReLU has been claimed to be more physiologically realistic as an activation function, more closely approximating the behaviour of actual neurons. Instead of a sigmoid-shaped activation, the action potential of biological neurons is simply a thresholding operation, akin to ReLU.

6. Due to its simplicity, computational effectiveness, and capacity to overcome some of sigmoid activation's drawbacks, ReLU is a popular option in many applications. But sigmoid activation still has benefits of its own, including offering a probabilistic interpretation and being helpful for jobs where outputs must be constrained between 0 and 1.

#### 2.3.4.2 Vanishing Gradient Problem

When training deep neural networks with specific activation functions, such as the sigmoid function, an issue known as the vanishing gradient problem may arise. The definition of the sigmoid function, sometimes referred to as the logistic function, is: f(x) = 1/(1 + exp(-x)) The sigmoid function's derivative is tiny at the function's extreme regions, which leads to the vanishing gradient issue [28]. The sigmoid function's derivative may be computed as follows: f'(x) = f(x) \* (1 - f(x))

Figure 2.1: Depicts Sigmoid function and it's derivative [29].

The sigmoid function approaches either 1 or 0, producing a tiny derivative, as the input goes away from zero in either the positive or negative direction as shown in Figure 2.1 [29]. The modest gradients that are back-propagated during training are doubled at each layer, which might lead to the gradients decreasing exponentially as they go backward through the network [30]. Hence, the early layers of the network experience extremely small gradients, which significantly decelerates convergence or even prevents it altogether.

Deep neural networks with sigmoid activation may find it challenging to learn long-range relationships and recognise complicated patterns in the input due to the vanishing gradient problem [31]. Activation functions that do not have the vanishing gradient problem, such as rectified linear units (ReLU) or its derivatives such as Leaky ReLU and Parametric ReLU, are preferred in practise as a result of this restriction. These alternate activation functions enable for more efficient gradient propagation during back-propagation since they feature non-zero gradients for positive inputs. Consequently, sparse activation functions help address the challenge of vanishing gradients and enable the training of deeper neural networks.

## 2.4 Review of Neural Networks Design

Recent years have seen substantial advancement in Very Large Scale Integration (VLSI) architecture for Neural Networks (NNs). This section comprehensively summarises current research on VLSI design for NNs, emphasising significant advancements and difficulties encountered. The section discusses many facets of hardware acceleration, energy efficiency, memory organisation, and algorithmic improvements in VLSI design for NNs. Furthermore, it examines future research possibilities and emphasises how these breakthroughs have affected practical applications. Numerous applications, including robotics and autonomous vehicles, as well as natural language processing and image identification, have been transformed by neural networks [32]. However, there is an increasing need for effective hardware designs to expedite the execution of NNs as they become more complicated and demanding in terms of computing needs [33]. Multiple components are integrated on a single chip in VLSI design, which improves performance, energy efficiency, and scalability.

### 2.4.1 Artificial Neural Networks

#### CNNs

Convolutional Neural Networks (CNNs) are commonly employed for image and video processing tasks. Current research efforts have been dedicated to enhancing CNN designs by incorporating techniques such as parallel processing, and weight pruning and hardware architectures like systolic arrays that are used to implement certain algorithms efficiently [34]. These optimization approaches have led to significant advancements in terms of accelerated computation and reduced power consumption in CNN implementations.

#### RNNs

Recurrent Neural Networks (RNNs) are beneficial for sequential data processing tasks such as speech recognition and language translation. Recent research has

prioritized the development of hardware acceleration techniques, such as folding, pipelining, and parallel processing, to enable real-time applications while minimizing power consumption [35]. These advancements aim to enhance the efficiency and performance of RNN-based systems in various language-related tasks.

#### **SNNs**

Spiking Neural Networks (SNNs) are well-suited for tasks that involve eventdriven processing, as they closely emulate the behavior of biological neurons. To enhance the processing capabilities and energy efficiency of SNNs, researchers have introduced innovative VLSI architectures. These include spike-based learning mechanisms and event-driven hardware designs. These novel approaches aim to optimize the functionality of SNNs, enabling more effective processing while conserving energy resources.

## 2.4.2 Energy-Efficient VLSI Architectures

The battery life of mobile devices and the amount of power used by data centres are both directly impacted by energy efficiency, making it a crucial factor in the design of VLSI for NNs [36]. In order to reduce energy consumption while preserving acceptable accuracy levels, researchers have investigated strategies including approximation computing, voltage scaling, clock gating, low-power digital circuits, and approximate computing.

## 2.4.3 Memory Organization Techniques

In NN calculations, memory access and data transfer are the main bottlenecks. Researchers have suggested a variety of memory organisation strategies to overcome this, including data reuse, sparsity exploitation, and hierarchical memory architectures [37]. These methods seek to improve data storage efficiency, decrease memory access latency, and boost performance as a whole.

## 2.4.4 Algorithmic Innovations

Along with hardware improvements, algorithmic advancements have also had a big impact on NN VLSI architecture [38]. To lessen the complexity of NN models without significantly sacrificing accuracy, researchers have investigated meth-

ods including quantization, pruning, and compression. These methods allow for resource-constrained VLSI chips to be implemented effectively.

## 2.4.5 Impact on Real-World Applications

Numerous real-world applications have been significantly impacted by the developments in NN VLSI architecture. They have aided in the development of voice assistants that can comprehend natural language, real-time object identification in driverless cars [40], picture analysis for medical diagnosis, and many more fields [39]. The breadth of ML applications has been broadened, and user experiences have been improved thanks to the increased efficiency and performance of VLSIbased NN implementations.

## 2.4.6 Conclusions for Neural Network Design

The deployment of NNs in a wide variety of applications is now possible because of impressive breakthroughs in the field of VLSI design for neural networks. Researchers have significantly improved the field through advances in memory organization, hardware acceleration methods, energy-efficient designs, and algorithmic optimizations. The future of ML will continue to be shaped by more studies in this field, which will encourage the creation of hardware designs for neural networks that are smarter, quicker, and more energy-efficient.

# CHAPTER 3 Implementation of Neural Network Architectures

In this chapter, we discuss the implementation of all the three architectures, including aspects of micro-architecture, SISO, MISO and MIMO. Implementations of adder and multiplier are also illustrated.

## 3.1 Implementation of Adder

Adders are the fundamental building blocks of complicated digital circuits. The layout of this entire adder unit determines the circuit's performance. One of the key performance factors for many digital circuits is the circuit's operating speed, which ultimately depends on the basic adder unit's delay. The delay of the adder circuit has been the subject of extensive investigation. This research study presents an improved version of the carry increment adder (CIA) aimed at enhancing the circuit's delay performance [41]. The enhancement is made by replacing the ripple carry adder (RCA) used in the previous design of the CIA with a carry look adder (CLA). For comparison analysis, simulation research is conducted.

The speedier carry look ahead modules are suggested in this study as a substitute for the significantly slower ripple carry adder in a modified carry increment adder. Although we only implemented the design for two 8-bit binary additions in this study, it might be expanded to a higher-order adder circuit. Fastevolving biomedical equipment, common wireless and mobile gadgets, and compact, portable devices use high-performance VLSI systems more frequently. Innumerable measures have been taken to decrease the ripple carry adder's latency, area, power usage, and other drawbacks. Architecture of carry increment adder is shown in Figure 3.1.

Figure 3.1: Depicted the architecture of a carry increment adder (CIA).

## 3.2 Implementation of Multiplier

The Baugh-Wooley multiplier is a type of parallel multiplier used in digital circuits, specifically designed for signed binary numbers. It is known for its simplicity and efficient implementation in hardware. The modified Baugh-Wooley multiplier is a variation of the original algorithm that aims to improve its performance and reduce the number of partial products generated during the multiplication process. The modified Baugh-Wooley multiplier is particularly well-suited for Very Large Scale Integration (VLSI) architecture, as it can be implemented efficiently in hardware. Architecture of MBW is shown in Figure 3.2. Here's a brief explanation of the VLSI architecture implementation of the modified Baugh-Wooley multiplier:

Input and Data Representation: The modified Baugh-Wooley multiplier takes two signed binary numbers A and B as inputs. These numbers are typically represented using two's complement notation. The size of the inputs will determine the number of bits in each input and the resulting product. For instance, if the inputs are n-bit numbers, the product will be a 2n-bit number.

Partitioning the Inputs: The inputs A and B are partitioned into three segments each: positive, negative, and zero segments. For each input, these segments di-

Figure 3.2: Architecture of Multiplier.

vide the bits based on the sign and value of the bit (positive, negative, or zero). Generation of Partial Products: In the traditional Baugh-Wooley algorithm, the number of partial products generated is  $2n^2$  (where n is the number of bits in each input). The modified Baugh-Wooley algorithm aims to reduce this number for better efficiency. In the modified Baugh-Wooley multiplier, the partial products are generated only for the non-zero segments of both inputs. This reduces the number of partial products significantly compared to the traditional method. Partial Product Reduction: After generating the partial products, the next step is to sum them up to obtain the final product. The partial products are grouped and added together in an efficient manner to produce the final result. The reduction process involves techniques such as carry-save addition, carry-propagate addition, or Wallace tree-based adders to optimize the addition process and minimize the critical path delay. Overflow Handling:Care must be taken to handle overflow

and ensure the correct representation of the product, especially in cases where the product requires more bits than the original input size. Output:The output of the modified Baugh-Wooley multiplier is the product of the two input numbers, represented in signed binary format.

## 3.3 Implementation of SISO NN Architecture

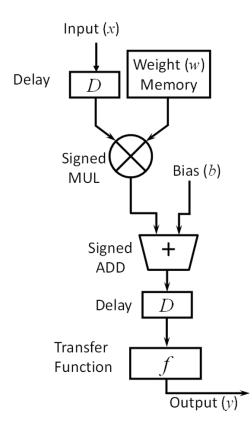

The SISO (Single-Input Single-Output) neural network architecture is designed to take a single-input value and produce a single-output value. Figure 3.3 shows the architecture of a SISO NN. The input is fed into a multiplier, then multiplied by weight value which is predefined in memory, and then the resulting output from the multiplier is then passed to an adder. In the adder, a bias value *b* is added to the output of the multiplier. The resulting value from the adder is then forwarded to the output through a transfer function.

Figure 3.3: SISO architecture.

For details, let's consider an input value, denoted as x, which is passed through a multiplier to be multiplied by a weight value, w. The resulting value from the multiplier is x \* w. Next, this value is fed into an adder where a bias, represented

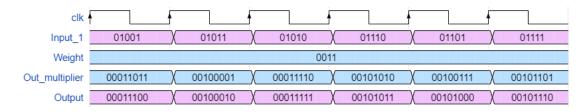

as *b*, is added to it. The output of the adder can be expressed as ((x \* w) + b). Subsequently, the resulting value is passed through a transfer function, and if it meets a certain threshold condition, it is forwarded to the output. In summary, the output can be described as ((x \* w) + b). Simulated waveform corresponding to above mentioned SISO architecture is depicted in Figure 3.4. This architecture is particularly useful when sequential processing of data is needed for 1-D signal processing such as gesture recognition, speech recognition, etc.

Figure 3.4: Depicted the simulated waveform obtained using SISO architecture.

## 3.4 Implementation of MISO NN Architecture

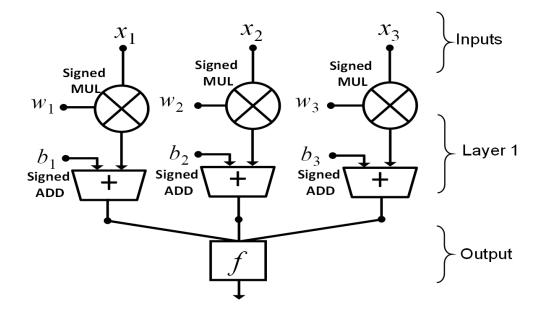

In this section, the implementation of a multiple-input, single-output (MISO) neural network design at the RTL level is demonstrated. The design takes into account the activation function, f to determine the signal that will advance. Both serial and parallel architectures can be utilized to construct the MISO architecture. In case of serial architecture, which is comparable to SISO architecture in 1-D data processing, more time is required to process data. However, when processing times are short, a parallel architecture is typically employed, allowing for the simultaneous processing of multiple inputs. The implementation of weights' memory is realized in the form of a Look-Up Table (LUT). The design is implemented at the RTL level using the Verilog hardware description language. Parallel Architecture of MISO is shown in Figure 3.5. Here x, w, and b represent the input vector, weight matrix, and bias vector, respectively. Subscript value represents input/output number.

Figure 3.5: Architecture of MISO.

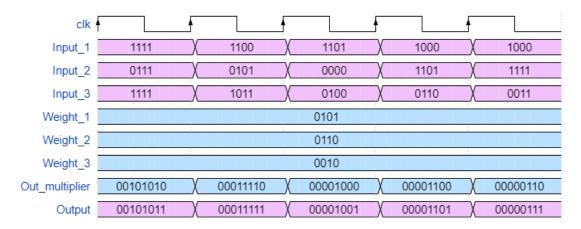

For more details, let's consider the input values x1, x2, and x3 which are fed to multiplier to get multiplied with the weight values say w1, w2, and w3, respectively. Then the outputs of multiplier are (xi \* wi), *i* ranging 1 to *n*. It goes to adder where we add a bias *b* to it so outputs of adder are (xi \* wi) + b. It is then fed to activation function and if it fulfils the threshold condition it moves ahead. Now the highest value which if greater than zero is sent to the output. So output is (xj \* wj) + b. as depicted with simulated waveform in Figure 3.6.

Figure 3.6: Simulated waveform obtained using MISO architecture.

## 3.5 Implementation of MIMO NN Architecture

MIMO (Multiple-Input Multiple-Output) networks can process many input streams simultaneously, such as video or picture frames captured from various angles or sensing modalities. This enables them to increase object identification precision by considering diverse viewpoints or sensor inputs. It can be also used for Natural Language Processing (NLP). To improve language comprehension and production, MIMO networks can handle a variety of information sources, including text, audio, and visual data. For instance, a MIMO network may use textual and contextual information to improve sentiment categorization in sentiment analysis.

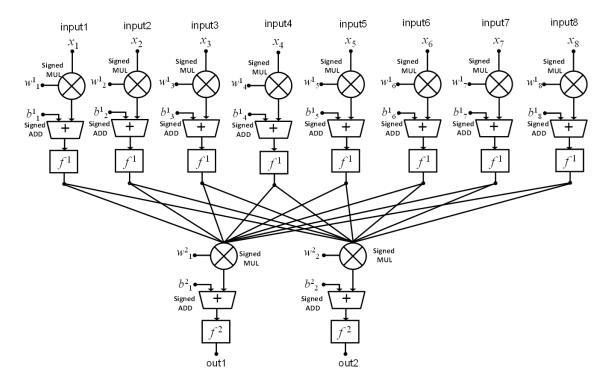

Figure 3.7 depicts the architecture design of a MIMO neural network, which has two layers and eight outputs (out1, out2) and inputs (x1, x2, ..., x8). Weight memory is made up of input-corresponding weight values. To choose which value needs to be transmitted at the output, weight values and inputs are provided to the ReLU neuron. A value from the data memory will be supplied to the output in accordance with the ReLU value. As previously mentioned, the signed adder and signed multiplier make up the neuron. Other elements of the architecture, such as the activation function and neuron (which include signed multipliers and signed adders as discussed in Chapter 2), are identical to those in the MISO architecture.

Figure 3.7: Depicted the developed MIMO Architecture.

For details, we considered a scenario where we have input values x1, x2, x3, x4, ..., x8. These inputs are passed through a multiplier, where they are multiplied with corresponding weight values w1, w2, w3, w4, ..., w8. The outputs of the multiplier can be represented as (x1 \* w1), (x2 \* w2), (x3 \* w3), (x4 \* w4), ..., (x8 \* w8). These outputs are then fed into an adder, where a bias value b is added to each of them. Consequently, the outputs of the adder can be expressed as ((x1 \* w1) + b), ((x2 \* w2) + b), ((x3 \* w3) + b), ((x4 \* w4) + b), ..., ((x8 \* w8) + b). The next step involves passing these values through an activation function, where they are checked against a threshold condition. If the condition is met, the values proceed further in the process.

Finally, the two largest values, which are greater than zero, are selected and sent to the output. These values can be denoted as ((xj \* wj) + b)and((xk \* wk) + b). In summary, the input values are multiplied with corresponding weights, then added with a bias, and passed through an activation function. The two largest values meeting the threshold condition are chosen as the outputs. Figure 3.8 illustrates the simulated waveform generated by MIMO architecture.

| clk      |          | , j          |          |            |          |

|----------|----------|--------------|----------|------------|----------|

| Input_1  | 1111     | ( 1100 )     | ( 1101   | χ 1000     | 1000     |

| Input_2  | 0111     | ( 0101 )     | 0000     | χ 1101     | 1111     |

| Input_3  | 1111     | ( 1011 )     | 0100     | χ 0110     | 1000     |

| Input_4  | 0110     | ( 1000 )     | ( 1000   | χ 1101     | 0011     |

| Input_5  | 0101     | ( 0001 )     | 1010     | χ 1000     | 0011     |

| Input_6  | 0001     | ( 0010 )     | 1000     | χ 0101     | 0011     |

| Input_7  | 0010     | ( 1101 )     | (1110    | χ 1011     | 0011     |

| Input_8  | 0011     | (0110)       | (1111    | χ 1111     | 01000    |

| Output_1 | 00100100 | (00011000)   | 00001100 | X 00011001 | 00010101 |

| Output_2 | 00100011 | ( 00001010 ) | 00000000 | χ 00010010 | 00010010 |

Figure 3.8: Simulated responses of MIMO architecture.

# CHAPTER 4 Neural Networks Layout

As mentioned earlier, three neural network architectures have been implemented, covering the entire process from RTL (Register Transfer Level) to GDSII (Graphic Data System version II), utilizing open-source tools. The following discussion will delve into the design flow employed for tape-out generation, the tools utilized in this process, the tape-outs for each of the three architectures, and the corresponding parameters associated with them. Before delving into these details, let's first explore the concept of tape-out and the advantages of employing open-source technologies.

In the realm of VLSI (Very Large Scale Integration), the term tape-out refers to the physical design phase of an integrated circuit (IC). It involves the intricate positioning and routing of various components such as interconnects, capacitors, resistors, and transistors onto the surface of the chip. The tape-out design phase plays a critical role in determining the performance, power consumption, and reliability of the chip. It represents a crucial stage in the overall design process of integrated circuits (ICs). The tape-out design process begins with a circuit schematic or netlist, which specifies the logical connections between the components of the circuit. This serves as the initial step for the tape-out design.

Following that, the components are placed on the chip's surface, and the designer routes the interconnects between them to create a physical representation of the circuit.

### 4.1 **Design Flow**

RTL Design: The RTL description of the chip is first created using a hardware description language (HDL), such as Verilog or VHDL. This description provides a higher-level definition of the circuit's behaviour and functioning. The gate-level netlist is created by synthesising the RTL code. In order to develop a gate-level representation of the circuit, synthesis entails translating the RTL description to a library of standard cells and optimising the design for area, power, and time. The location of the chip's primary components and their relative placements on the silicon die is determined by the floorplan, which is developed in this step. In floorplanning, variables including chip size, cell count and type, power distribution, and I/O positioning are taken into account. Placement: This process establishes the precise location of each chip cell. The positions are optimised to reduce wire length, timing errors, and power usage. In order to identify the best answer, placement algorithms employ strategies like simulated annealing, genetic algorithms, or analytical approaches. Clock Tree Synthesis (CTS): To maintain perfect synchronisation and slight clock skew, CTS requires creating an optimised clock distribution network throughout the chip. To balance the clock tree and adhere to timing specifications, it inserts buffers and buffers. During the routing step, metal rails are used to link the chip's components and nets (interconnections). The wire length is optimised, design rules and limitations are met, and signal route conflicts are resolved. The general routing structure is decided by global routing, while the final connectivity is carried out by detailed routing. Physical Verification: During physical verification, the layout is examined for design rule violations (DRC) to make sure it complies with the foundry-specified production restrictions. It comprises inspections for width, overlap, spacing, and other regulations to guard against potential manufacturing problems. Timing Analysis: To make sure the chip complies with the given timing limitations, timing analysis assesses the timing routes in the design. It takes into account things like the circuit's delays, setup and hold times, and clock frequency. To confirm timing at various design phases, static timing analysis (STA) is used. Power Analysis: Power analysis calculates the chip's power use and indicates potential areas for power optimisation. Examining the switching activity and power distribution within the design assists in lowering power consumption and mitigating thermal concerns. The final GDSII layout file is created once the design has been confirmed to fulfil all necessary requirements. The placements, forms, and layers of each component are all included in the geometric representation of the chip that is contained in the GDSII file.

### 4.2 Design Tools

Synthesis: RTL synthesis is performed by yosys/ABC. OpenSTA: Creates timing reports by doing static timing analysis on the generated netlist. Floorplanning: initfp - Specifies the rows (used for placement) and tracks (used for routing), as

well as the core area for the macro.Places the macro input and output ports using ioplacer. Creates the power distribution network (pdngen). Inserts welltap and decap cells into the floorplan using tapcell. Placement: RePLace performs global placement. Resizer: Resizing is an optional design optimization. OpenDP: Performs detailed placement to legalize the globally placed components. Synthesises the clock distribution network (the clock tree) using TritonCTS. Routing: FastRoute - Creates a guide file for the detailed router by doing global routing performs thorough routing with TritonRoute Performs SPEF extraction with Open-RCX

| RTL Implementation | Modelsim                           |  |

|--------------------|------------------------------------|--|

| Synthesis          | Yosys, OpenSTA                     |  |

| Floor planning     | init_fp, ioplacer, pdngen, tapcell |  |

| Placement          | RePlace, Resizer, Open DP          |  |

| CTS                | TritonCTS                          |  |

| Routing            | Fastroute, Tritonroute, OpenRCX    |  |

| Tape-out           | Magic                              |  |

| Sign-off           | Magic, Netgen, CVC                 |  |

Figure 4.1: Tools used for implementation.

GDSII : The final GDSII layout file is generated by Tapeout Magic based on the routed definition. As an alternative option, KLayout can also generate the final GDSII layout file from the routed definition. The Signoff process includes performing Design Rule Checks (DRC) and Antenna Checks, which are done using Magic and KLayout in conjunction. Netgen is utilized for performing Layout versus Schematic (LVS) Checks. Additionally, Circuit Validity Checks are conducted by CVC. Figure 4.1 illustrates the design flow and corresponding tools used for this work. Detailed discussion on tools will be seen in next sub-section.

## 4.3 Details of Tools Used

OpenROAD: OpenROAD is an all-encompassing digital design pipeline that includes placement, optimisation, and routing tools. For phases in floorplanning, placement, and routing [43].

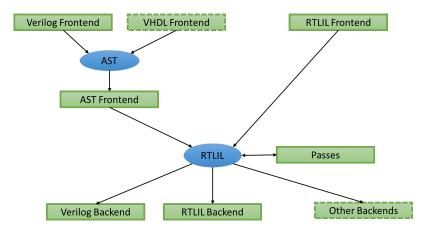

yosys: Yosys functions as a Verilog HDL synthesis tool, taking a high-level behavioral design description as its input and producing an output in the form of RTL, logical gate, or physical gate level descriptions of the design. Its primary strengths lie in behavioral and RTL synthesis. Yosys offers a wide array of commands, referred to as synthesis passes, enabling a diverse range of synthesis tasks across behavioral, RTL, and logic synthesis domains. The architecture of Yosys is designed for extensibility, making it a suitable foundation for creating custom synthesis tools tailored to specific tasks. Yosys employs two distinct internal formats. The first format is utilized for storing an abstract syntax tree (AST) representation of a Verilog input file. This format is referred to as AST and is generated by the Verilog Frontend component. Subsequently, this AST is processed by a module called the AST Frontend, which transforms it into Yosys' principal internal format known as RTLIL (Register-Transfer-Level Intermediate Language) representation. This conversion involves performing various simplifications within the AST representation prior to generating the RTLIL structure from the simplified AST data. The RTLIL representation serves as the common input and output format for all Yosys passes, offering several advantages over employing distinct formats for various stages: Passes can be reorganized or modified by adding/removing them. Passes can efficiently preserve unchanged design components without format conversions, as Yosys passes maintain the same data structure and execute modifications directly. A uniform interface is maintained across all passes, streamlining comprehension of Yosys source code and facilitating feature augmentation. The RTLIL representation encompasses features beyond a standard netlist: Internal cell library with predefined functional cells for RTL datapath, registers, and logical gate-level elements. Accommodation for multi-bit values employing wire bits and constants for coarse-grained netlist representation. Support for fundamental behavioral constructs like conditional statements and multi-case switches with output update sensitivity. Capability for multi-port memories. However, the use of RTLIL also presents a drawback as it maintains a high-level format across all passes, even when dealing with gate-level synthesis that doesn't require advanced features. For simplicity in passes targeting low-level representations, these passes inspect RTLIL input for utilized features and halt if unsupported high-level constructs are detected. In such cases, a preliminary pass that translates higher-level constructs into lower-level equivalents must be invoked before synthesis. Yosys, an open-source, extensible hardware synthesis tool, caters to designers seeking a universally accessible, vendor-independent synthesis solution. It also appeals to